世事洞明皆学问

thedairygame

2020.12.14 星期一 晴

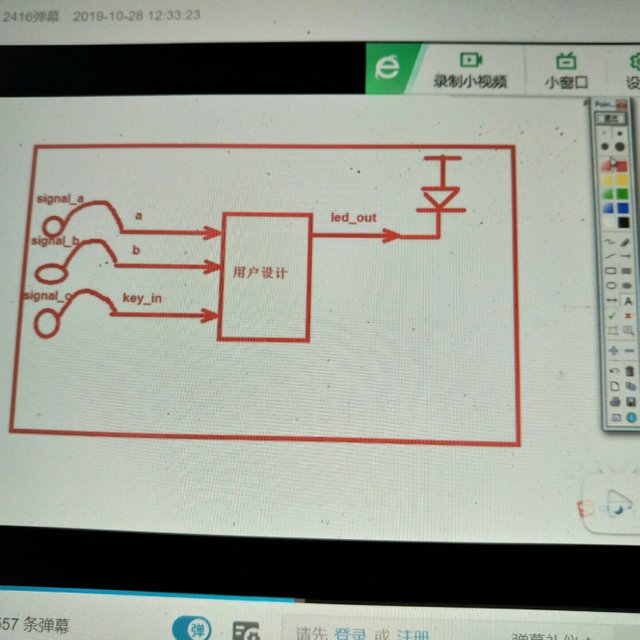

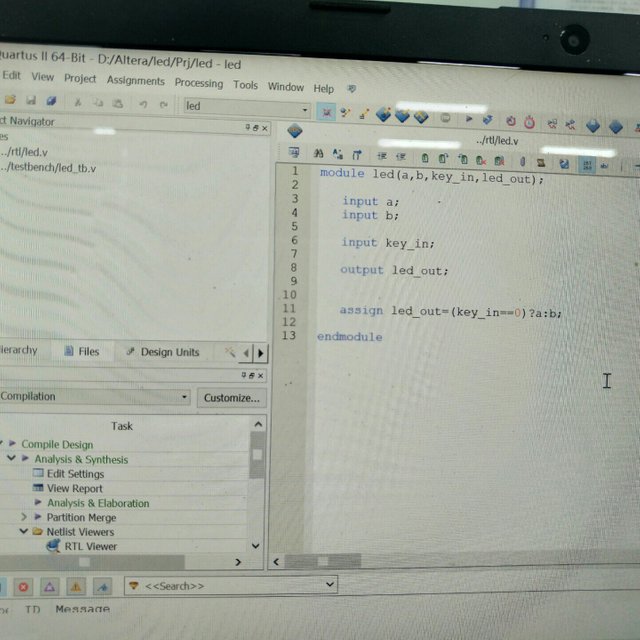

梅哥的FPGA工程结构真是让我感到惊艳,原来FPGA工程也可以这样做。层次清晰,重点突出。doc用于存储说明文档,Prj用于存储工程文件,rtl用于存储工程源码,testbench用于存放测试文件。

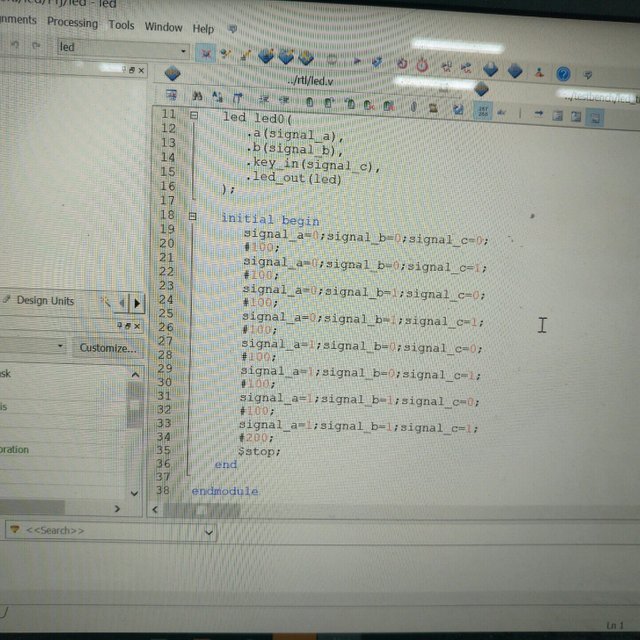

源码就是我们所构建的模型,而测试文件就是将模型实例化并添加激励文件,从而观察输出是否正确。

功能仿真就是寄存器级别的仿真,不涉及时序,又叫RTL级仿真,时序仿真又叫门级仿真,加入了竞争冒险以及延迟特性,更符合实际。

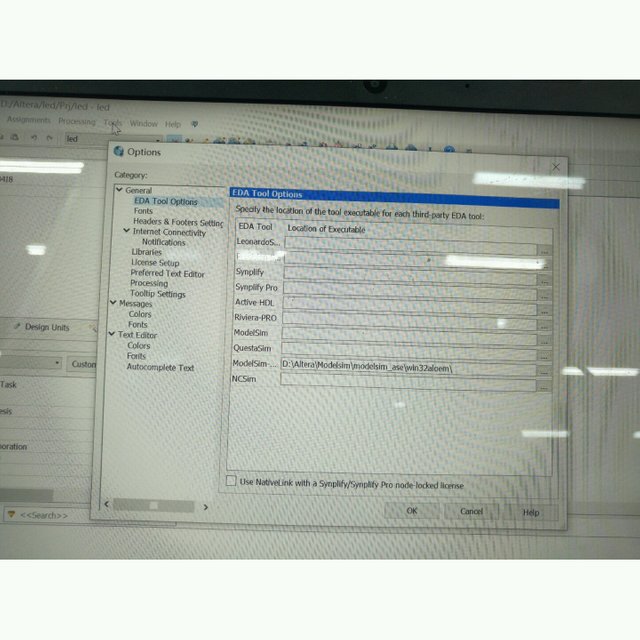

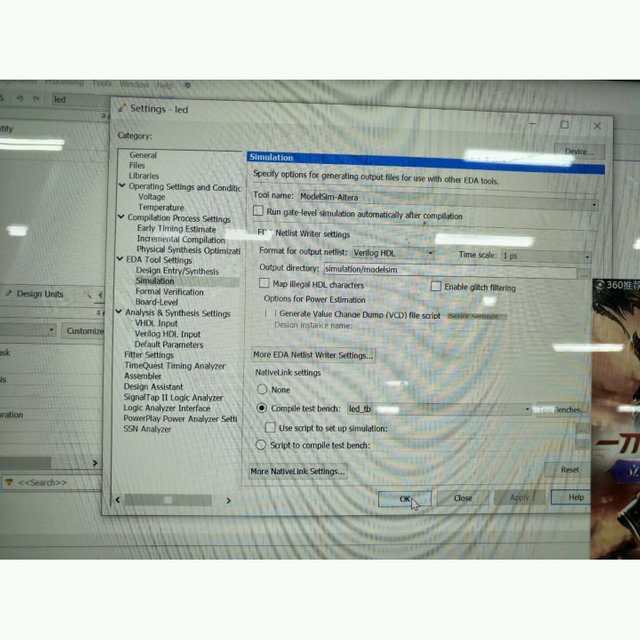

使用modelsim-altera进行仿真,需要在quartus II里指定modelsim-altera的程序路径,同时需要在assignments→settings里进行仿真设置。然后,编译,仿真,并点击RTL simulation按钮,就会自动得到RTL仿真波形。点击gate level simulation仿真按钮就会得到门级仿真波形,含有延迟和竞争冒险现象。

由波形可知,输出会有一段延迟时间,约10.457ns,200ns处b和c会产生翻转竞争冒险,b如果先翻转会产生一个高电平脉冲,延迟10.877ns后输出,脉冲宽度0.398ns,300ns处的输出被延迟了11.275ns,400ns处也存在竞争冒险,致使10.877ns延迟后输出,脉冲宽度为0.467ns,500ns延迟11.275ns后输出,600ns处亦存在竞争冒险,但幸好没有不期望波形出现。

也有人问我,什么是竞争冒险?那让我下次告诉您吧😄

[WhereIn Android] (http://www.wherein.io)

#cn #the1000daysofsteem #thediarygame #dblog #zzan #freewrite #writing #cnstm #cn-malaysia #education #cn-curation #technology #cn-reader #steemexclusive