Smart ESP #1

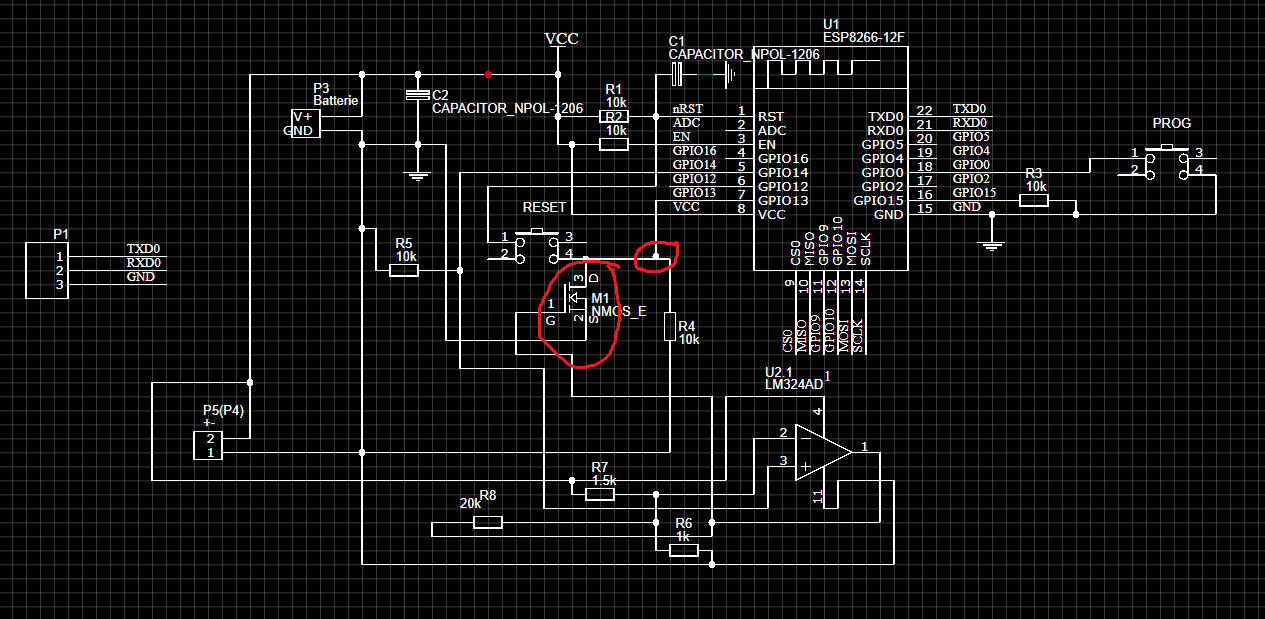

Es geht also im folgenden darum, das der ESP sich selbst an einem Reset hindert. Dies geschieht indem ein Mosfet die Reset-Kopplung nach GND unterbricht. Damit dies klar und eindeutig geschieht habe ich mich für einen logischen Fet entschieden. Solange die Gate-Spannung nicht klar über den Schwellwert geht, schaltet er nicht durch. Hier kam es jetzt zu dem Problem, dass ich einen Verarmungstyp gebraucht hätte. Warum? Nun, im Sleep Mode ist keiner der ESP Outputs auf high. Wie sollte also der Fet den Reset zulassen und durchschalten wenn das Gate nicht high wird. Ich habe also einen invertierenden Schmidt-Trigger dimensioniert und bestehend aus ein paar Widerständen und einem OPV auf die Platine gebracht. Dieser invertiert den Eingang zum Fet. Nicht sehr elegant, aber versucht mal einen Verarmungstypen mit logischer Funktion zu bekommen.

Wenn nun das Gate Low ist, wird der Zustand des Buttons über GPIO 13 eingelesen. In der Zeichnung ergibt das einen Spannungsteiler. Ich habe im Nachhinein R4 halbiert um ein sicheres Low bzw High zu kriegen.

Congratulations @geblendert! You received a personal award!

Click here to view your Board

Congratulations @geblendert! You received a personal award!

You can view your badges on your Steem Board and compare to others on the Steem Ranking

Vote for @Steemitboard as a witness to get one more award and increased upvotes!